### **PATENT MONITOR** Advanced Packaging

**Quarterly Report**

Q4 2022

#### **TABLE OF CONTENTS**

#### **INTRODUCTION & METHODOLOGY** 3 Context Scope of the patent monitoring service Methodology and segments definition Companies tracked in this patent monitoring service **MAIN TRENDS** 11 Time evolution of patent publications over the past decade Fan Out packaging Silicon interposer Embedded interconnect bridge Hybrid bonding 3D stacked memories **QUARTER OVERVIEW** 16 Key facts of the quarter Patent families newly published and granted in the quarter

Patents expired or abandoned in the guarter Main IP collaborations (patent co-filings) Main IP transfers (change in patent ownership) US IP litigations open or closed New EP oppositions PLAYERS IP ACTIVITY DURING THE QUARTER 24 **Pure play foundries** 25 TSMC

GlobalFoundries

#### **OSATs**

|                                                                                                                                           | Sa |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| OSATs<br>Amkor<br>ASE<br>SPIL<br>JCET<br>Nepes<br>Powertech Technology<br>Deca<br>Huatian Technology<br>SJSemi<br>Tongfu Microelectronics |    |

| IDMs<br>Samsung<br>Infineon<br>Intel<br>Micron<br>SK Hynix<br>YMTC                                                                        | 40 |

| NDE                                                                                                                                       | 40 |

NPE Xperi

#### ANNEX 50

48

## INTRODUCTION 8 METHODOLOGY

#### INTRODUCTION Context

2.5D/3D stacking and fan-out WLP are promising solutions to meet the needs of the semiconductor packaging It is crucial to monitor patent activity and IP strategies of key semiconductor packaging players.

In the semiconductor industry, there is a growing demand for integrating more compute and memory within a single package in order to achieve since a factors and improve product performance. However, Moore's Law becomes increasingly difficult to achieve as node advancement reaches its limits. As a result, the process of chip miniaturization has been slowing down. Advanced packaging techniques, such as 2.5D & 3D stacking, and fan-out wafer level packaging, have emerged as crucial solutions to meet the needs of the semiconductor industry. These new approaches allow for the integration of multiple dies into a single package, with the possibility of combining mature and advanced nodes, and they have supplemented the dominant flip-chip (FC) and wire-bond (WB) technologies. The roadmap for these advanced packaging technologies is challenging and the supply chain is becoming increasingly competitive, with the demand for high-density fan-out (HD FO) redistribution layers (RDLs), high-density input/output interconnections (I/O), and advanced interconnect technologies such as silicon interposer, embedded bridge, hybrid bonding, and chiplets approach.

The market for **2.5/3D packaging** shows the most potential for growth, with 3D SoC technology growing the most driven by the increasing popularity of hybrid bonding for chiplets 3D integration. In the fan-out WLP industry, the segment experiencing the highest growth is the ultra-high density fan-out (UHD FO), which has emerged as a more cost-effective solution compared to silicon interposers. Semiconductor packaging was primarily performed by OSATs such as **ASE/SPIL**, **Amkor**, **JCET**, etc. and they continue to play an important role in this field. However, it is **TSMC**, **Samsung** and **Intel** that have been developing innovative 2.5D/3D packaging solutions such as silicon interposer, embedded bridge, and hybrid bonding. By offering advanced back-end solutions and using their front-end capabilities, these companies poised to influence future technology and intellectual property (IP) developments in this area.

In this context, it is crucial to monitor patent activity and intellectual property (IP) strategies of key players. Such knowledge can assist in understanding your competitors' R&D roadmap and strategies, evaluate the risks, and detect business opportunities.

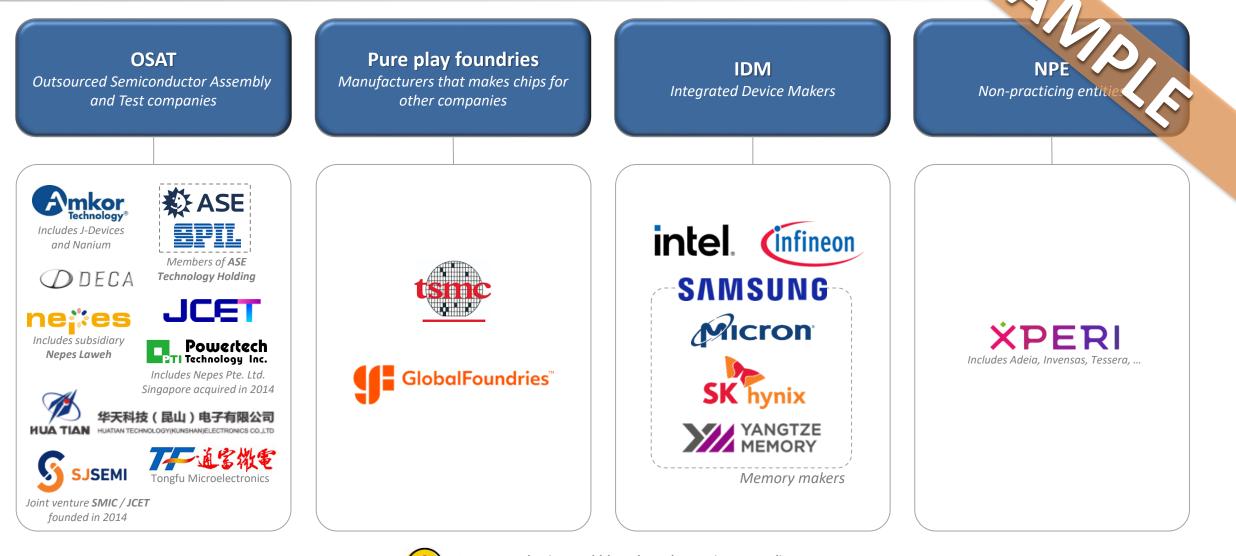

The Advanced Packaging Patent Monitor gives periodic insights on the IP activity of a selection of key companies: TSMC, Intel, Samsung, Amkor, ASE, SPIL, JCET, Deca, Nepes, Powertech (PTI), SJSemi, Tongfu (TFME), Huatian, Infineon, Micron, SK Hynix, YMTC, GlobalFoundries, and Xperi/Adeia.

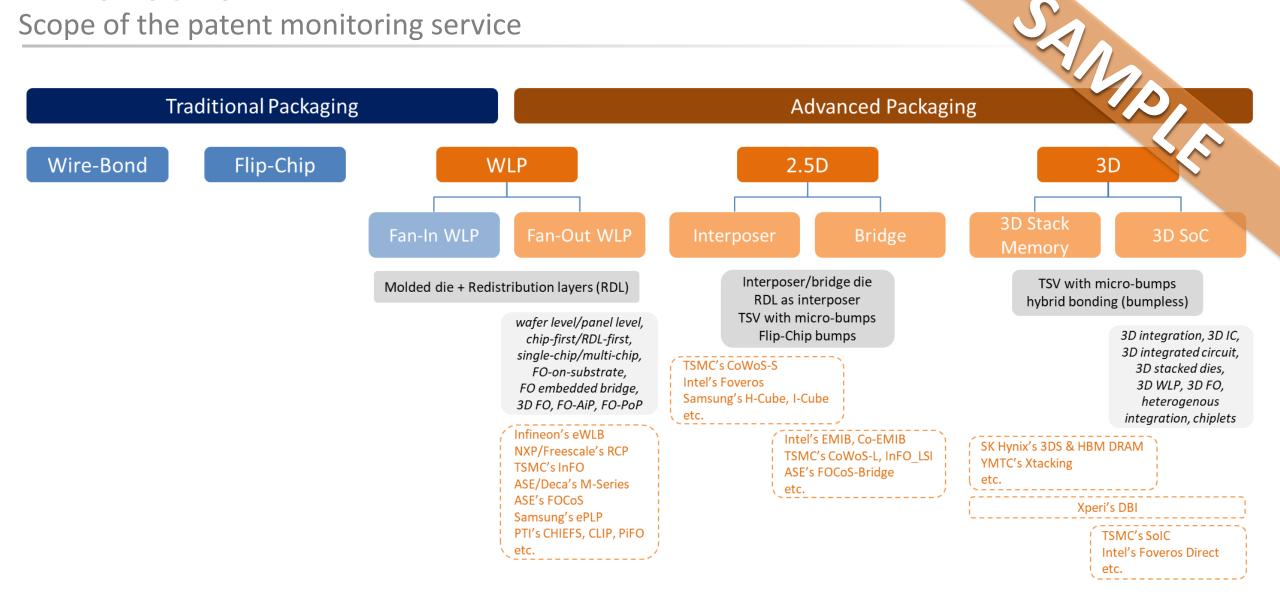

#### **INTRODUCTION** Scope of the patent monitoring service

#### **INTRODUCTION** Methodology and segment definition

- The data are extracted from the FamPat worldwide patent database (ORBIT Intelligence) which provides 100+ million patent documents from 100 pater (USA, Japan, Europe, China, Korea, Taiwan, Hong Kong, Singapore, etc.).

- Patent families are manually segmented into three main categories of advanced packaging (fan-out WLP/PLP packaging, 2.5D & 3D integration, other packaging) and dimension of the segments (Si interposer, Si bridges, hybrid bonding, etc.). A patent family can belong to multiple technical or sub-segments.

- > Three types of patents are selected: new patent families (i.e., new inventions), patent families granted for the first time, and patents newly expired or abandoned.

- > Four types of legal events are monitored: US litigations, European oppositions, IP collaborations (i.e., patent co-filings), and transfer of IP rights (i.e., change in patent ownership).

#### **TECHNICAL SEGMENTATION**

#### Fan-out packaging (FO)

- Wafer level packaging (FO-WLP)

- Panel level packaging (FO-PLP)

Includes Fan Out 2.5D/3D and Fan Out Package-on-Package (FO-PoP)

#### 2.5D/3D IC (heterogeneous integration, chiplets)

- Interposer/bridge (silicon interposer, embedded interconnect bridge)

- Hybrid Bonding (i.e., direct metal-to-metal and oxide-to-oxide bonding without bumps)

- 3D-stacked memory (excludes multiple single memory cells fabricated on a same wafer)

#### Others

Includes

- Traditional packaging (flip-chip, fan-in, chip scale packaging, SoC, etc.)

- Packaging that consists of a combination of several packages (Package-on-Package).

Note that Fan-Out PoP is included in Fan-Out packaging segment

- FAB equipment and materials that may be used in packaging

- Data processing / computing enabled by multiple packaged electronics components

#### LEGAL STATUS

**New patent families** Patent family published for the first time during the quarter

**New granted patent families** Patent family granted for the first time during the quarter

New dead patents Patents expired or abandoned (revoked, lapsed) during the quarter

#### LEGAL EVENT

Patent litigation (US) and oppositions (Europe) IP collaborations (i.e., patent co-filed by different entities) Transfer of IP rights (i.e., change in patent ownership) when data are available

Technical segments will be adapted over time according to the technological evolution of advanced packaging

#### KnowMade

#### INTRODUCTION

#### Companies tracked in this patent monitor

Company selection could be adapted over time according to the ecosystem evolution of advanced packaging

#### PATENT MONITOR

Take advantage of quarterly updates on IP activities

#### CONTENTS

#### Quarterly IP database (Excel file)

- New patent families (inventions)

- Patent families granted for the first time

- Patents newly expired or abandoned

- Transfer of IP rights (re-assignment, licensing)

- Patent litigations and oppositions

- Patents categorized by technology, supply chain segment, application, etc.

#### Quarterly IP report (PDF slide deck)

- Key fact & figures of the quarter

- Graphs and comments covering the patent landscape evolutions

- A close look at the key IP players, newcomers, and key patented technologies

#### Access to IP analyst (100h per year)

• Q&A session and discussion with our IP analysts regarding the quarterly report results, trends, analyses, specific patented technologies or companies' patent portfolios in the field of the patent monitor.

#### WHY YOU SHOULD SUBSCRIBE

- ✓ Track your **competitors**, partners or clients

- ✓ Identify **newcomers** to your technology field

- $\checkmark$  Early detect **opportunities** and risks for your business strategy

- ✓ Be ahead of technology trends

- ✓ Identify emerging research areas and **cutting-edge technology** developments

- ✓ Mitigate patent infringement risks

- ✓ Take advantage of free technologies

#### **PATENT MONITOR** Quarterly report

On a quarterly basis, this report will provide the IP trends over the last three months, with a close look to key patented technologies from a selection of key players:

TSMC, Intel, Samsung, Amkor, ASE, SPIL, JCET, Deca, Nepes, Powertech Technology, SJSemi, TFME, Huatian, Infineon, Micron, SK Hynix, YMTC, GlobalFoundries, Xperi

✓ Main patent applicants, their notable patent filings and technologies.

Ase BPIL

(C)KnowMade

Powertech JCET DECA

TELERE GISEM

intel SAMSUNG SK hvoix

Infineon Micron WANGTZ

Samsung Group

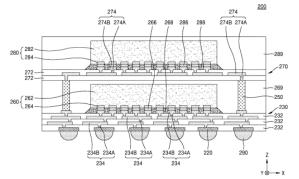

04-2022 IP ACTIVITY

mber of patent families. A p

Patent families newly granted

atents expired or abandoned

une foundry service develop

The interposer fabrication is

yer is positioned inside and

gas foaming agent may be u

functionalizing the interp

Warpage. Warpage control is chips, and a mold, filling the s

the interposer substrate (US

Mold reliability. The molding resulting in voids. Samsung up

KnowMa

ASE

Q4-2022 IP ACTIVITY

umber of patent families.

Patent families newly granted

Patents expired or abandoned

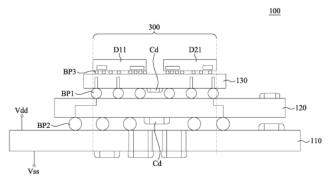

ASE is active in the field of hybrid bo

Superior bonding strength and elecontact is addressed in US20220

US20230027674 a method allows to bonding process. A surface treatment

be significantly reduced by embeddi decoupling capacitor, such as a deep die by a shorter electrical path (US20

family can belong to multiple

New patent families

(inventions)

KnowMod

04 2022

64

YMTC

Fan-out

Q4-2022 IP ACTIVITY

New patent families

nventions)

ber of patent families.

Patent families newly granted

atents expired or abandone

FO - Panel

lew patent families (inventions)

IP collaborations (patent co-filings)

IP transfers (change in ownership

US litigations

EU opposition

atent families newly granted atents expired or abandoned **XPERI**

- ✓ New entrants and their patents.

- ✓ Technology trends and notable patented technical solutions.

- $\checkmark$  Key patents newly granted, their owners and claimed inventions.

- ✓ Main IP right transfers (reassignments, licensing agreements).

- ✓ Key patents newly expired or abandoned, their owners and their potential market impact.

- ✓ Noteworthy news on patent litigation and opposition, plaintiffs and defendants, patents and products involved.

SAMSUNG

**ASE**

YANGTZE

#### **PATENT MONITOR** Quarterly IP database

#### Segments

(an X indicate a patent belonging to the segment)

|                               |                                              |                                          |                                                |                                                    |                                                |                                                                 |                                           |                                                         |                        |                                    |                                                           |                               | REAS                                 | ON OF SELE         | CTION               |                       | Fan Out F                                                        | Packaging                                      |                                                 | 2.5D/3D                |                   |      |        |

|-------------------------------|----------------------------------------------|------------------------------------------|------------------------------------------------|----------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------|------------------------|------------------------------------|-----------------------------------------------------------|-------------------------------|--------------------------------------|--------------------|---------------------|-----------------------|------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------|------------------------|-------------------|------|--------|

| estel unique<br>nily ID (FAN) | Current assignees<br>of the patent<br>family | Re-assignments                           | Publication<br>numbers of the<br>patent family | Title                                              | Abstract                                       | Claims                                                          | Current legal<br>status of the<br>patents | Earliest<br>publication date<br>of the patent<br>family | Earliest grant<br>date | Expected expiry<br>date            | Biblio summary<br>(link to updated<br>online<br>database) | Ne <del>v</del><br>inventions | New<br>granted<br>patent<br>families | Ezpired<br>patents | Patent<br>transfers | Patent<br>litigations | All fan-out<br>packaging<br>(wafer<br>level &<br>panel<br>level) | Fan out<br>panel level<br>packaging<br>(FOPLP) | All<br>2.5D/3D<br>packaging<br>technologie<br>s | Interposer<br>/ Bridge | Hybrid<br>bonding |      | Others |

| 103771997                     | SEMICONDUCTOR                                |                                          | US202310231<br>US20230052136                   | Thermoelectric                                     | An integrated circuit                          | (0320230002136)<br>What is claimed is:                          | PENDING                                   | 2022-12-13                                              |                        | 2042-06-07                         | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                | x                                               | ×                      | x                 |      |        |

| 103770513                     |                                              | FROM 2021-12-08 TO                       | F#202577589<br>US20230048536                   | ເບລະບະວິບັນຈີນິວຣາ<br>Interconnect with            | ്പ്രിട്ടായ്ട്ടാൽക്കാട്ട്ര<br>A method includes | (បំទ <u>20230048036)</u><br>What is claimed is:                 | LUS20250745036Anj<br>PENDING              | 2022-12-13                                              |                        | (US20250745936A))<br>2042-01-03    | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | x      |

| 103769814                     | SEMICONDUCTOR                                |                                          | DE102022118524                                 | <u>Qu'szuzstu468117'</u><br>Backside               | ເບລະບະ່ວນບ4່ອງກາງ<br>The present               | ເບລີ່2ບໍ່230ປັ່ນຈີສ້າງ<br>1. A structure,                       | US2025674557AA)<br>PENDING                | 2022-12-09                                              |                        | (JS2025674557(A))<br>2042-06-29    | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | x      |

| 103687839                     | SEMICONDUCTOR                                | CHARG(32/0510An);<br>FROM 2022-01-18 TO  | 17@202384689*<br>US20230041839                 | (0820230041833)<br>Hybrid Node Chiplet             | The present                                    | (US20Z30041855)<br>What is claimed is:                          | (0520230041533A1)<br>PENDING              | 2022-12-06                                              |                        | (0520230041535A1)<br>2042-05-24    | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                | x                                               | x                      |                   |      |        |

| 03620749                      |                                              | FROM 2022-04-11 TO                       | F&20230036280                                  | (OS20230036280)<br>Seal Ring Structure             | "(0520230036260)"<br>The present               | ເບລີ່2ບີ້2ວັບບໍລິຄົຊັ່ຈບງ<br>What is claimed is:                | US20250036280Anj<br>PENDING               | 2022-12-16                                              | 2022-12-16             | (US20250036280A))<br>2042-05-05    | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | x      |

| 103618124                     |                                              | 2021-11-22 TO 2021-11-                   | DE102022102731                                 | (0320230030605)<br>Dram computation                | A memory circuit                               | ຳເບີຣວນຊຸຣິນບຣູບໍ່ຮູບບາ<br>1. A memory circuit                  | (US2023863887UA))<br>PENDING              | 2022-11-22                                              |                        | (US20230630670UA))<br>2042-01-31   | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                | x                                               | x                      |                   |      |        |

| )3530388                      | SEMICONDUCTOR                                | CHANG; FROM                              | "F@202308031"<br>KR10-2023-0015830             | (0520230026676)<br>Semiconductor                   | (05/20/2300/26676)<br>The present              | (US20Z30026676)<br>What is claimed is:                          | (0520230026676A1)<br>PENDING              | 2022-12-06                                              |                        | (D52023002667/6A1)<br>2042-01-07   | Open                                                      | ×                             |                                      |                    |                     | . 1                   |                                                                  |                                                | x                                               | x                      |                   |      | _      |

| 3529025                       | SEMICONDUCTOR                                |                                          | DF#2023008630<br>US20230023353                 | (US20230023303)<br>Semiconductor die               | A die dipping                                  | 10820230023505j<br>What is claimed is:                          | (8520230029373A1)<br>PENDING              | 2022-11-22                                              |                        | (D520230023333A1)<br>2042-02-22    | Upen                                                      | Identif                       |                                      |                    |                     |                       |                                                                  |                                                | x                                               | x                      |                   | x    |        |

| 03528982                      |                                              | LAKSANA, CHIPTA<br>PRIYA: FROM 2022-     | FM2053769805<br>US20230023268                  | (diszüzető)<br>Dicing Process in                   | TUS202300232667<br>A method includes           | ເປລຂົບຂຶ້ວເບັບວິວເຊື່ອງ<br>What is claimed is:                  | US20250723268A                            | 2022-11-25                                              |                        | (US20250723266A))<br>2042-03-15    | Open                                                      | - New                         | patent                               | ts app             | licatio             | ns                    | x                                                                |                                                | x                                               | x                      |                   |      | _      |

| 03422764                      |                                              | CHARTER WERP-CHART,<br>EBOM 2022-04-28   |                                                | Pate                                               | ent info                                       | rmatio                                                          | U (S20250027000A))<br>PENDING             |                                                         | 2022-12-20             | (US20250027000A))<br>2042-05-06    |                                                           | - Pater                       | nts nev                              | vlv gra            | anted               |                       |                                                                  |                                                |                                                 |                        |                   |      |        |

| 03420378                      | SEMICONDUCTOR                                | CHER, CAIA4AAU;<br>EBOM/2022-03-02-      | Th@18033300                                    | (ບອຂີ່ນີ້ຂ້ອຍບຳຈີ່ແອງ                              | (ບຣ່ະບະ່ວຍປາ4ອາດ)                              | 10.52023001431371                                               |                                           |                                                         | 2023-05-21             | (032/0230014913A1)<br>2042-03-04   |                                                           | - Pater                       |                                      |                    |                     | doner                 | 4                                                                | Da                                             | tont                                            | cog                    | menta             | tion |        |

| 03324632                      |                                              | (ASSIg                                   |                                                |                                                    | A second contract of the second second         |                                                                 |                                           | egal statı                                              | ls,                    | (JS202500121074A)<br>2042-01-19    |                                                           |                               |                                      |                    |                     | uonet                 |                                                                  | Fa                                             | Lent                                            | Segi                   | пепта             | CION |        |

| 03324429                      |                                              | 00,00420,00450520;<br>FBOM 2021-08-16 TO | TF#2023800                                     | perlink to                                         | updated                                        | online d                                                        | atabase)                                  |                                                         |                        | (7053202300179323A))<br>2041-10-07 | Open                                                      | - Trans                       |                                      |                    | its                 |                       |                                                                  |                                                |                                                 |                        |                   |      | ×      |

| 03323778                      | MANUSACENDING                                | PAN, PHILEX MING-<br>YAN: FROM 2022-01-  | TW202318146                                    | Local interconnect<br>(0320230010037)<br>Method of | (082023000037)<br>A sustem includes: a         | (0320230010037)<br>1. A system for                              | US20250010357Anj<br>PENDING               | 2022-11-01                                              |                        | (US20250070357A)<br>2042-02-24     | Open                                                      | - Pater                       | nt litiga                            | ation              |                     |                       |                                                                  |                                                | v                                               |                        |                   | ×    | -      |

| 03323526                      | MANUSACENDING                                |                                          | TF#20230370#1<br>US20230010038                 | "(Usztiż 300 bluste) - "<br>Vafer Bonding          | (USZUZ3001003%)<br>Vafer bonding               | (US202300i0038)<br>What is claimed is:                          | (0520230015058A1)<br>PENDING              | 2022-11-04                                              |                        | (US20230015058A1)<br>2041-09-10    | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                | ~                                               |                        | ×                 |      |        |

| 03254483                      | MICRON                                       | 2021-00-14 TTVD IN                       | CN/18182211                                    | (Chizistezzho)<br>Semiconductor                    | (CN218182271)<br>The utility model             | what is claimed is:<br>ເປົ້ານີ້2To1822ກິງ<br>1. A semiconductor | (CN195005400A)<br>(CN218182211UU)         | 2022-11-04                                              | 2022-12-30             | (CN19505400A)<br>(CN218182211UU)   | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                | ^                                               |                        | ^                 |      | x      |

| 03251801                      | TECHNOLOGY<br>LINQU SAMSUNG                  |                                          | CN115535387                                    | - tchanoodoodry<br>Package                         | (CN10030387)<br>The invention                  | 1. A semiconductor<br>(Chanobooosi)<br>1. The utility model     | GRANTED<br>(CN115535387A)                 | 2022-12-30                                              | EVEL-12-00             | 2032-07-08<br>(CN115535387A)       | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | x      |

| 03251801                      | ELECTRONICS<br>HUATIAN                       |                                          | CN115547970                                    | ່າງເວາຍາວອາກົອາດ)                                  | "                                              | าารูเปล่าอองการ/ช่า                                             | PENDING<br>(CN115547970A)                 | 2022-12-30                                              |                        | 2042-10-09<br>(CN115547970A)       |                                                           |                               |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      |        |

|                               | TECHNOLOGY                                   |                                          | CN115551121                                    | Silicon-based gallium                              | The invention                                  | 1. The utility model<br>ាយកៅរបស់ពីខ្លីព្រ                       | PENDING<br>(CN115551121A)                 |                                                         |                        | 2042-10-11<br>(CN115551121A)       | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | x      |

| 03240708                      |                                              |                                          |                                                | Apparatus and                                      | The present                                    | 1. An apparatus,<br>(CNZ10102174)                               | PENDING<br>(CN218182174UU)                | 2022-12-30                                              | 0000 40 05             | 2042-06-20<br>(CN218182174UU)      | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | X      |

| 03239348                      | INTEGRATED                                   |                                          | CN218182174                                    | (CN218183493U)                                     | The utility model                              | 1. The utility model<br>[CNI218763435]                          | GRANTED<br>(CN218183493UU)                | 2022-12-30                                              | 2022-12-30             | 2032-08-30<br>(CN218183493UU)      | Open                                                      | x                             |                                      |                    |                     |                       | x                                                                |                                                |                                                 |                        |                   |      | x      |

| 03238465                      | SEMICONDUCTOR                                |                                          | CN218183493                                    | Earphone assembly                                  | The utility model<br>ເຜດການໍວິຈອບບວງ           | 1. An earphone<br>(ლიითაზსია)                                   | GRANTED<br>(CN115548003A)                 | 2022-12-30                                              | 2022-12-30             | 2032-08-22<br>(CN115548003A)       | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | x      |

| 03237482                      | SEMICONDUCTOR                                |                                          | CN115548003                                    | Semiconductor                                      | The invention relates                          | 1. A semiconductor                                              | PENDING                                   | 2022-12-30                                              |                        | 2041-06-30                         | Open                                                      | x                             |                                      |                    |                     |                       |                                                                  |                                                |                                                 |                        |                   |      | x      |

The patents are **manually categorized in technical segments** using keyword analysis of patent title, abstract and claims, in conjunction with expert review of the subject-matter of inventions.

## MAIN TRENDS

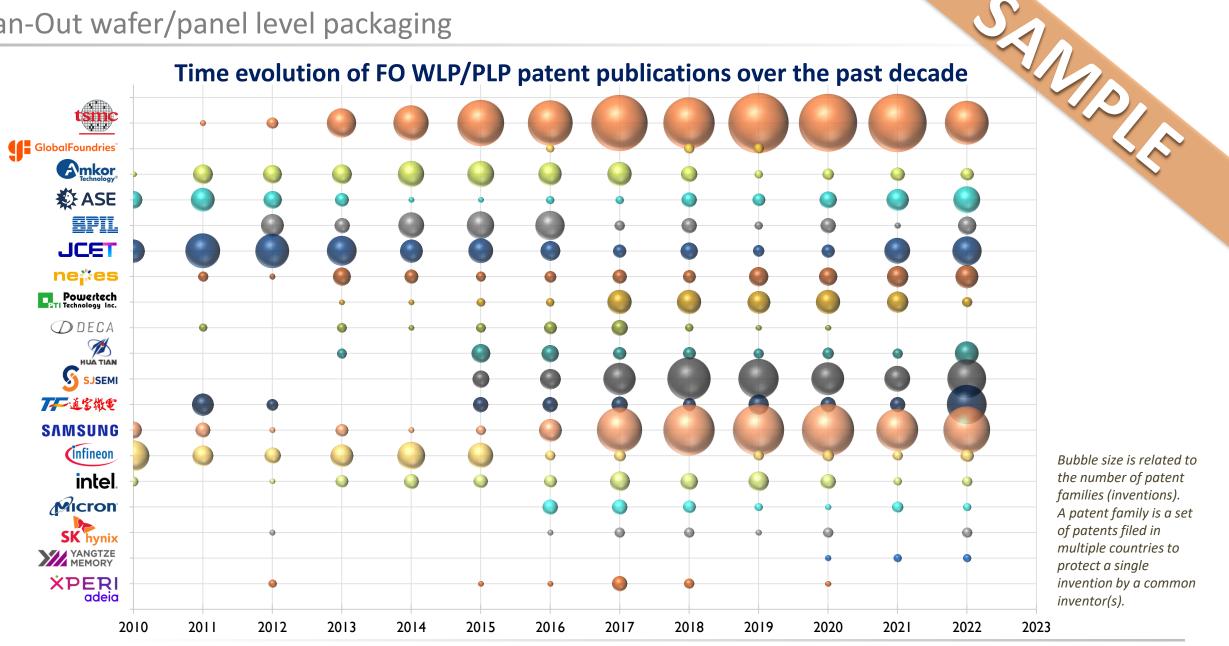

#### **MAIN TRENDS** Fan-Out wafer/panel level packaging

(C)KnowMade

Advanced Packaging – Patent Monitor | Quarterly Report | Q4 2022 © 2022 All rights reserved | www.knowmade.com

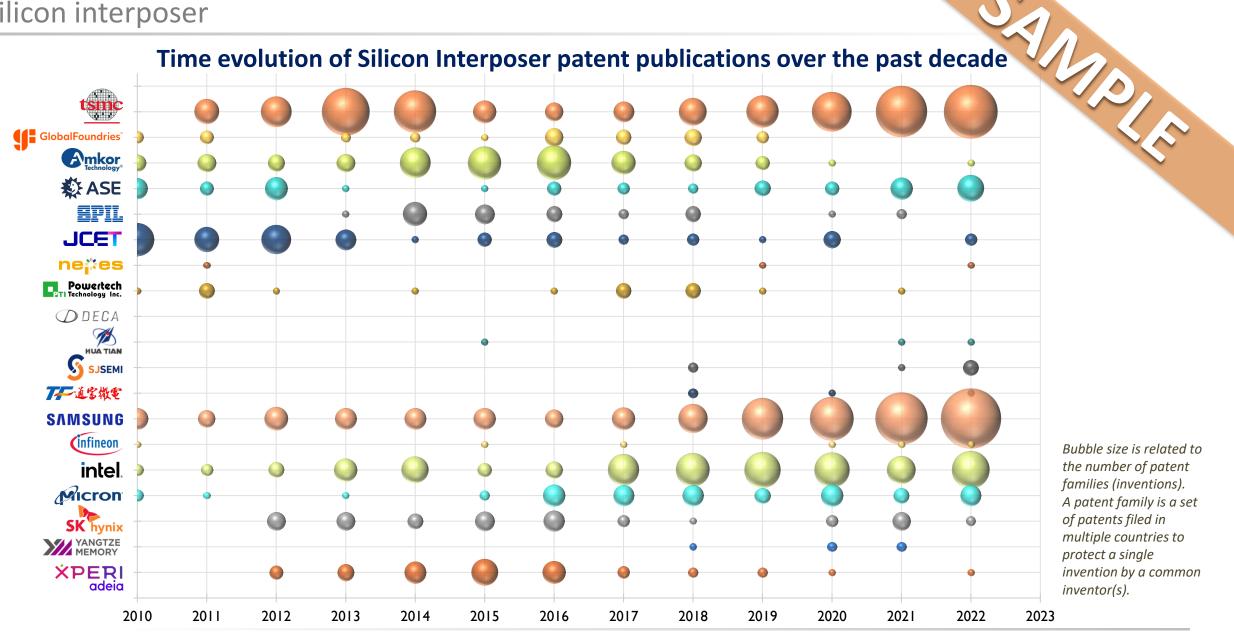

#### **MAIN TRENDS** Silicon interposer

(C)KnowMade

Advanced Packaging – Patent Monitor | Quarterly Report | Q4 2022 © 2022 All rights reserved | www.knowmade.com

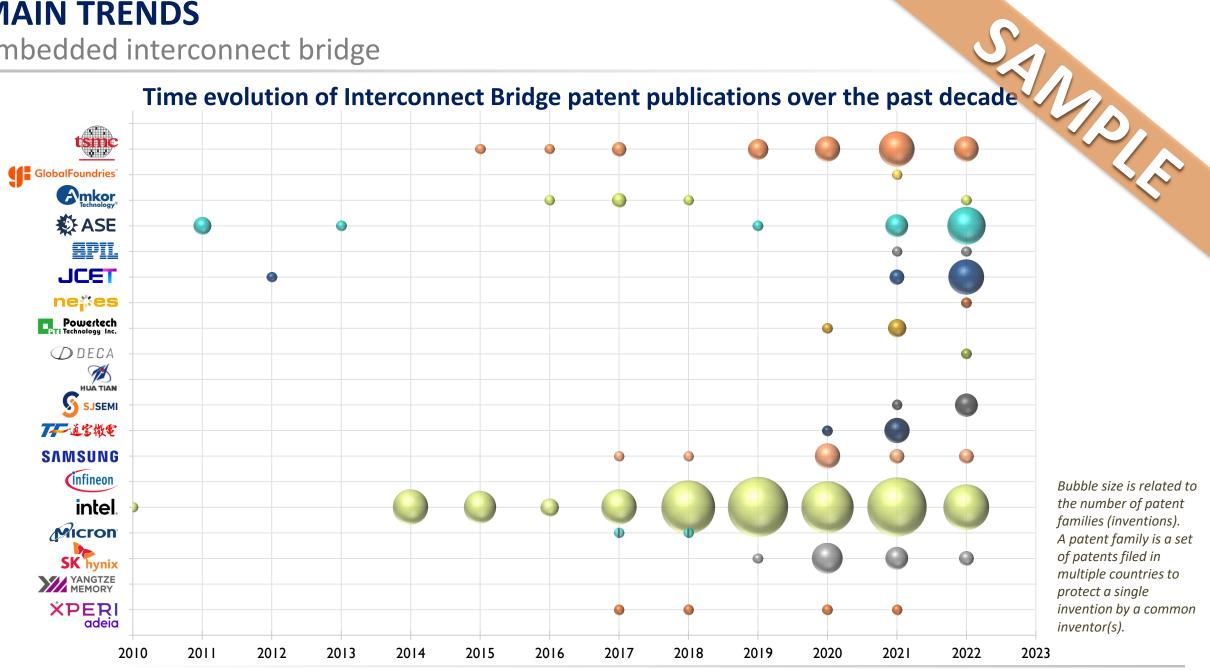

#### **MAIN TRENDS** Embedded interconnect bridge

(C)KnowMade

Advanced Packaging – Patent Monitor | Quarterly Report | Q4 2022 © 2022 All rights reserved | www.knowmade.com

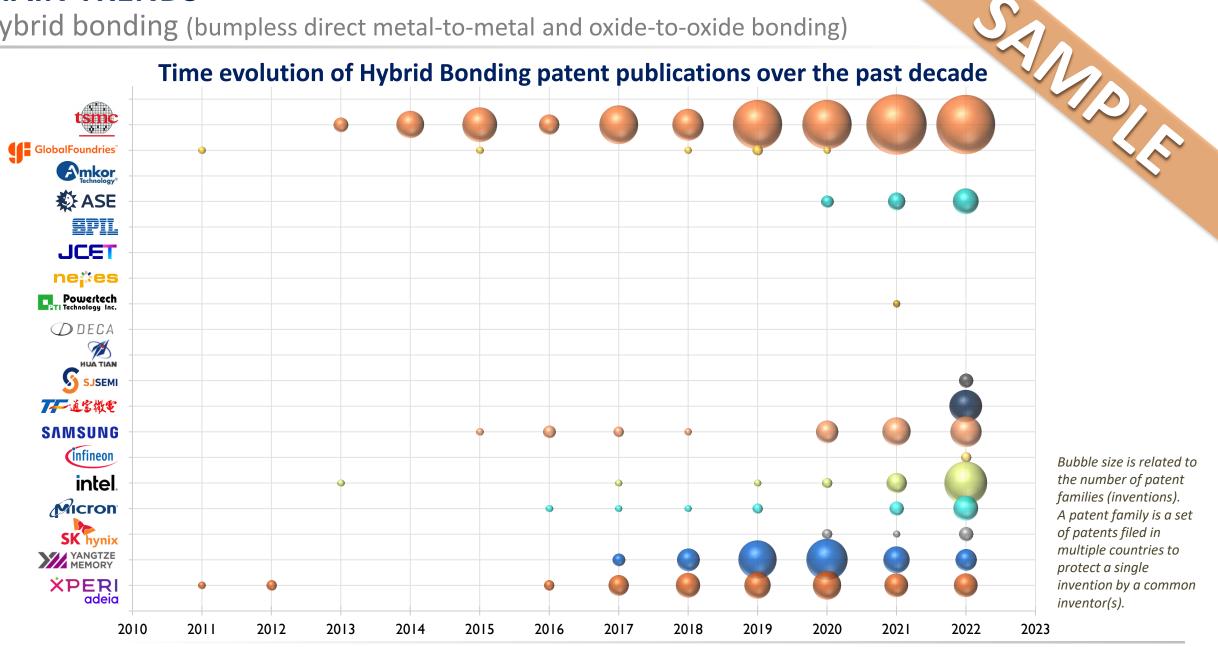

#### **MAIN TRENDS**

Hybrid bonding (bumpless direct metal-to-metal and oxide-to-oxide bonding)

(C)KnowMade

Advanced Packaging – Patent Monitor | Quarterly Report | Q4 2022 © 2022 All rights reserved | www.knowmade.com

# QUARTER OVERVIEW

#### Q4 2022 OVERVIEW Key facts

| SJSEMI NUA TIAN                    |            |                                         |                                                |                                          |                        |                   |                      |        |

|------------------------------------|------------|-----------------------------------------|------------------------------------------------|------------------------------------------|------------------------|-------------------|----------------------|--------|

|                                    |            | Fan Out I                               | Packaging                                      | ckaging 2.5D/                            |                        |                   |                      |        |

|                                    | Q4<br>2022 | All fan-out<br>packaging<br>(WLP & PLP) | Fan out panel<br>level<br>packaging<br>(FOPLP) | All 2.5D/3D<br>packaging<br>technologies | Interposer /<br>Bridge | Hybrid<br>bonding | 3D stacked<br>memory | Others |

| New patent families (inventions)   | 963        | 101                                     | 9                                              | 340                                      | 276                    | 59                | 105                  | 564    |

| Patent families newly granted      | 583        | 65                                      | 3                                              | 175                                      | 138                    | 36                | 47                   | 371    |

| Patents expired or abandoned       | 1008       | 67                                      | 0                                              | 68                                       | 60                     | 32                | 3                    | 881    |

| IP collaborations (new co-filings) | 5          | 0                                       | 0                                              | 1                                        | 0                      | 0                 | 1                    | 4      |

| IP transfers (change in ownership) | 1          | 0                                       | 0                                              | 0                                        | 0                      | 0                 | 0                    | 1      |

| US litigations                     | 0          | 0                                       | 0                                              | 0                                        | 0                      | 0                 | 0                    | 0      |

| EU oppositions                     | 0          | 0                                       | 0                                              | 0                                        | 0                      | 0                 | 0                    | 0      |

#### **Q4 2022 OVERVIEW** Patent families (inventions) newly published and newly granted

| <u>Note</u> : the numbers represent the number of <b>patent families</b> . | Detent                      | Detert                      |                    | Fan Out                       | Packaging          |                         |                    |                        |                    | 2.5D/3D I        | ntegration         |                  |                    |                  | 2             |       |

|----------------------------------------------------------------------------|-----------------------------|-----------------------------|--------------------|-------------------------------|--------------------|-------------------------|--------------------|------------------------|--------------------|------------------|--------------------|------------------|--------------------|------------------|---------------|-------|

| A patent family can belong to multiple segments.                           | Patent<br>families<br>newly | Patent<br>families<br>newly |                    | t packaging<br>& panel level) |                    | anel level<br>g (FOPLP) |                    | D packaging<br>ologies | Interpose          | er / Bridge      | Hybrid             | bonding          | 3D stacke          | d memory         |               | hers  |

| Patent assignees                                                           | published                   |                             | Newly<br>published | Newly<br>granted              | Newly<br>published | Newly<br>granted        | Newly<br>published | Newly<br>granted       | Newly<br>published | Newly<br>granted | Newly<br>published | Newly<br>granted | Newly<br>published | Newly<br>granted | Ne<br>publish | Inted |

| Intel                                                                      | 243                         | 155                         | 1                  | 7                             |                    |                         | 134                | 71                     | 123                | 69               | 19                 | 3                | 30                 | 18               | 109           | 83    |

| Samsung Group                                                              | 205                         | 128                         | 30                 | 14                            | 8                  | 1                       | 76                 | 27                     | 61                 | 16               | 6                  | 1                | 27                 | 11               | 111           | 91    |

| TSMC                                                                       | 161                         | 76                          | 15                 | 24                            |                    | 1                       | 81                 | 46                     | 64                 | 34               | 22                 | 20               | 36                 | 13               | 80            | 21    |

| ASE                                                                        | 64                          | 49                          | 4                  | 6                             |                    |                         | 9                  | 10                     | 9                  | 7                |                    | 4                |                    |                  | 52            | 35    |

| JCET Group                                                                 | 47                          | 10                          | 9                  | 2                             |                    |                         | 4                  | 1                      | 4                  | 1                |                    |                  |                    |                  | 36            | 8     |

| Huatian Technology                                                         | 39                          | 19                          | 10                 | 5                             |                    |                         | 1                  |                        | 1                  |                  |                    |                  |                    |                  | 28            | 14    |

| Infineon                                                                   | 39                          | 28                          |                    | 2                             |                    |                         | 1                  |                        | 1                  |                  |                    |                  |                    |                  | 38            | 26    |

| Micron                                                                     | 32                          | 29                          | 2                  |                               |                    |                         | 10                 | 6                      | 1                  |                  | 5                  | 2                | 4                  | 4                | 22            | 23    |

| YMTC                                                                       | 25                          | 6                           | 1                  |                               |                    |                         | 2                  | 1                      |                    |                  | 2                  | 1                |                    |                  | 22            | 5     |

| SJSemi                                                                     | 23                          | 10                          | 11                 |                               |                    |                         | 10                 | 3                      | 8                  | 3                | 2                  |                  | 3                  |                  | 6             | 7     |

| GlobalFoundries                                                            | 20                          | 22                          |                    |                               |                    |                         |                    |                        |                    |                  |                    |                  |                    |                  | 20            | 22    |

| Tongfu Microelectronics (TFME)                                             | 18                          | 16                          | 7                  | 1                             |                    |                         | 7                  |                        |                    |                  | 2                  |                  | 5                  |                  | 11            | 15    |

| SK Hynix                                                                   | 15                          | 10                          | 2                  |                               |                    |                         | 4                  | 2                      | 3                  | 2                | 1                  |                  |                    |                  | 6             | 7     |

| SPIL                                                                       | 10                          | 4                           | 4                  | 2                             |                    |                         | 1                  | 2                      | 1                  | 2                |                    |                  |                    |                  | 6             | 1     |

| Powertech Technology (PTI)                                                 | 7                           | 8                           | 1                  | 1                             |                    |                         | 1                  | 1                      | 1                  | 1                |                    |                  |                    |                  | 6             | 7     |

| Nepes                                                                      | 5                           | 2                           | 4                  | 1                             | 1                  | 1                       | 1                  |                        | 1                  |                  |                    |                  |                    |                  | 1             | 1     |

| Amkor Technology                                                           | 0                           | 2                           |                    |                               |                    |                         |                    |                        |                    |                  |                    |                  |                    |                  |               | 2     |

| Deca Technologies                                                          | 0                           | 1                           |                    |                               |                    |                         |                    | 1                      |                    | 1                |                    |                  |                    | 1                |               |       |

| Xperi/Adeia                                                                | 0                           | 5                           |                    |                               |                    |                         |                    | 5                      |                    | 3                |                    | 5                |                    |                  |               |       |

• Intel has been the most active patent applicant with 243 new patent families published this quarter, followed by Samsung and TSMC. For both, the focus is on Interposer/Bridge technologies. TSMC has strengthened its IP position in FO packaging and hybrid bonding with respectively 24 and 20 inventions newly granted.

• The 2022 Q4 IP activity of OSATs is more focus on 'others' segment, except for SJSemi which has been mainly active on FO and Interposer segments.

• Micron and the other memory makers published inventions related to hybrid bonding, which is an important process for memory device stacking.

• The non-practicing entity (NPE) Xperi did not publish any new invention this quarter, but it has been granted for new IP rights in hybrid bonding.

#### **Q4 2022 OVERVIEW** Expired and abandoned patents

Note: the numbers represent the

| number of <b>patents</b> . A patent can |                      |                                                      |                                          |                                       |                        |                |                   |        |

|-----------------------------------------|----------------------|------------------------------------------------------|------------------------------------------|---------------------------------------|------------------------|----------------|-------------------|--------|

| belong to multiple segments.            | Expired or           | Fan Out P                                            | ackaging                                 |                                       | 2.5D/3D                | Integration    |                   |        |

| Patent assignees                        | abandoned<br>patents | All fan-out packaging<br>(wafer level & panel level) | Fan out panel level<br>packaging (FOPLP) | All 2.5D/3D<br>packaging technologies | Interposer /<br>Bridge | Hybrid bonding | 3D stacked memory | Others |

| Samsung Group                           | 191                  | 4                                                    |                                          |                                       |                        |                |                   | 187    |

| TSMC                                    | 158                  | 23                                                   |                                          | 54                                    | 46                     | 32             |                   | 89     |

| Infineon                                | 126                  | 16                                                   |                                          | 5                                     | 5                      |                |                   | 105    |

| ASE                                     | 106                  |                                                      |                                          |                                       |                        |                |                   | 106    |

| GlobalFoundries                         | 77                   | 1                                                    |                                          |                                       |                        |                |                   | 76     |

| Intel                                   | 76                   |                                                      |                                          | 4                                     | 4                      |                | 3                 | 72     |

| Micron                                  | 73                   |                                                      |                                          | 4                                     | 4                      |                |                   | 69     |

| Amkor Technology                        | 45                   | 20                                                   |                                          |                                       |                        |                |                   | 25     |

| Powertech Technology (PTI)              | 22                   | 3                                                    |                                          |                                       |                        |                |                   | 19     |

| SPIL                                    | 21                   |                                                      |                                          |                                       |                        |                |                   | 21     |

| Xperi/Adeia                             | 16                   |                                                      |                                          |                                       |                        |                |                   | 16     |

| SK Hynix                                | 11                   |                                                      |                                          |                                       |                        |                |                   | 11     |

| JCET Group                              | 8                    |                                                      |                                          |                                       |                        |                |                   | 8      |

| Tongfu Microelectronics (TFME)          | 8                    |                                                      |                                          |                                       |                        |                |                   | 8      |

| Nepes                                   | 2                    |                                                      |                                          |                                       |                        |                |                   | 2      |

| Deca Technologies                       | 1                    |                                                      |                                          |                                       |                        |                |                   | 1      |

| SJSemi                                  | 1                    |                                                      |                                          |                                       |                        |                |                   | 1      |

| Huatian Technology                      |                      |                                                      |                                          |                                       |                        |                |                   |        |

| ҮМТС                                    |                      |                                                      |                                          |                                       |                        |                |                   |        |

- This quarter, **TSMC** is the player that has lost the most capacity to hamper the freedom of operate of its competitors in advanced packaging segments **FO**, **Interposer/Bridge** and **Hybrid Bonding**.

- The most important IP protection loss for Infineon is FO technology, with 16 patents expired this quarter for 2 new granted patents and no new published inventions.

- Amkor has lost 20 patents on FO this quarter while no new patent applications have been published in key packaging technologies.

#### **Q4 2022 OVERVIEW** Main IP collaborations (patent co-filings)

These table shows the main new collaborations on advanced packaging that have led to the co-filing of new patent applications involving on player we monitor in this Advanced Packaging Patent Monitor.

| Patent co-applicants                | Patent applications  | Title                                                                                                                                       | Segments          |  |  |

|-------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

| SAMSUNG ELECTRONICS<br>KPX CHEMICAL | <u>US20220350253</u> | Compositions for removing photoresists and methods of manufacturing semiconductor devices and semiconductor packages using the compositions | 2.5D/3D packaging |  |  |

| <b>TSMC</b><br>GLOBAL UNICHIP       | <u>US20230144129</u> | Semiconductor chiplet device                                                                                                                | 2.5D/3D packaging |  |  |

The inventive concept provides a photoresist-removing composition, which may cleanly remove a photoresist pattern used in a process of manufacturing a unit element, without adversely affecting (e.g., corroding) metal-containing components around the photoresist pattern. According to an aspect of the inventive concept, there is provided a photoresist-removing composition that includes a polar organic solvent, an alkyl ammonium hydroxide, an aliphatic amine not including a hydroxy group, and a monovalent alcohol.

The present disclosure relates to a semiconductor chiplet device, especially a structure in which multiple dies are connected through an interposer layer. The first die and the second die are configured to perform a data transmission through the first interface, the interposer layer and the second interface. the least one decoupling capacitor is arranged between the the first interface and the second interface, or is arranged in a vertical projection area of the first interface and the second interface on the packaging substrate.

#### **Q4 2022 OVERVIEW** Main IP transfers (change in patent ownership)

These table shows the main new IP transfers on advanced packaging that have led to the re-assignment of patent from/to at least one this Advanced Packaging Patent Monitor.

| IP transfer                                                        | Date | Transferred patent | Торіс                                                        | Segments          |

|--------------------------------------------------------------------|------|--------------------|--------------------------------------------------------------|-------------------|

| From Samsung Electro-Mechanics<br>To Kia Motors and Hyundai Motors |      |                    | Printed circuit board which may replace a silicon interposer | 2.5D/3D packaging |

|                                                                    |      |                    |                                                              |                   |

In October 2022, the IP rights of the patent <u>US11521922</u> owned by **Samsung Electro-Mechanics** were acquired by **Kia** and **Hyundai Motors**. The invention relates to a printed circuit board. The **interposer** market has been growing due to a high specification of a set and employment of a high bandwidth memory (HBM). Mostly, silicon has been used as a material for an **interposer**. For example, in the case of a semiconductor package using an **interposer**, a die may be surface-mounted on a **silicon interposer** and molded with a molding material. Due to the increase in the number of HBMs, an **interposer** has also been designed to have high performance, and accordingly, the difficulty of process may increase, and the issue of a lowered yield has emerged. An aspect of the present disclosure is to provide a printed circuit board which may easily implement a microcircuit pattern. Another aspect of the present disclosure is to provide a printed circuit board which may secure sufficient adhesive force between a microcircuit pattern and an insulating material. Another aspect of the present disclosure is to provide a printed circuit board which may replace a silicon interposer.

monitor in

#### **Litigations** US IP litigations open/closed during the quarter

#### No US IP litigation related to advanced packaging have been filed or closed in the quarter

No new oppositions have been filed at the EPO against packaging-related European patents

## 12 PLAYERS **IP ACTIVITY** DURING THE QUARTER

#### **Pure Play Foundries**

© 2022 All rights reserved | www.knowmade.com

#### **TSMC** Q4-2022 IP ACTIVITY

| Note: A patent family/patent can |         |                          |                     |                          |                        |                   |                      |    |  |

|----------------------------------|---------|--------------------------|---------------------|--------------------------|------------------------|-------------------|----------------------|----|--|

| belong to multiple segments.     | Q4 2022 | All Fan-Out<br>packaging | FO - Panel<br>level | All 2.5D/3D<br>packaging | Interposer<br>/ Bridge | Hybrid<br>bonding | 3D-stacked<br>memory |    |  |

| New patent families (inventions) | 161     | 15                       |                     | 81                       | 64                     | 22                | 36                   | 80 |  |

| Patent families newly granted    | 76      | 24                       | 1                   | 46                       | 34                     | 20                | 13                   | 21 |  |

| Patents expired or abandoned     | 158     | 23                       |                     | 54                       | 46                     | 32                |                      | 89 |  |

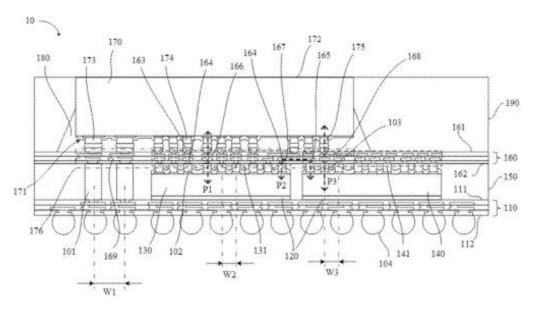

• In Q4-2022, the IP activity of TSMC is addressing all segments in the scope of this monitor, except for the very specific FO-Panel level segment.

- In FO packaging segment, this quarter TSMC's new patent application addressed thermal management, warpage and stress control, and reliability.

- Warpage/stress control: Structural engineering is favored by TSMC. In the new patent application <u>US20230066370</u>, a conductive pattern with an ellipse-like shape and a conductive via shifted outward result in stress reduction. In the <u>US20220352060</u>, a stacked via structure is capable of minimize the via the crack issue resulted from concentrated stress. The introduction of dummy dies (new granted patent <u>US11515268</u>), wall structure (new patent application <u>US20220406729</u>), and a ring-shaped dummy die (new patent application <u>US20220367383</u>) is also key to control structural stress. Material choice is also important. In the new granted patent <u>US11482497</u>, the CTE difference between the encapsulant and the encapsulant layer is chosen to be less than the CTE difference between the encapsulant and the semiconductor substrate of the die.

- Heat management: In the new granted Taiwanese patent TWI788025, TSMC claim InFO packages including thermal dissipation blocks (pending US patent application US20230037331).

Electrical reliability: In the new patent application <u>US20230067826</u>, via structures are made of conductive material with lower hardness.

The redistribution layer structure is easier to land over the via structure, and the via structure profile may be well-controlled. The bridge defects may be reduced, and the electrical failure may be prevented.

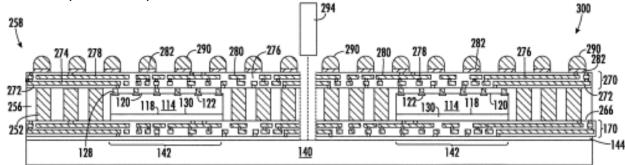

#### **TSMC** Q4-2022 IP ACTIVITY

- **TSMC** was the most active in the 2.5D/3D, especially for Interposer/Bridge.

- Heat management: An interposer containing line-shaped interposer is disclosed in the new patent application <u>US20220406723</u>. The line-shaped via may argument of the shaped via may argument of the shaped via improves power integrity and thermal performance.

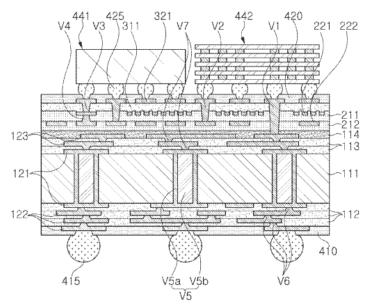

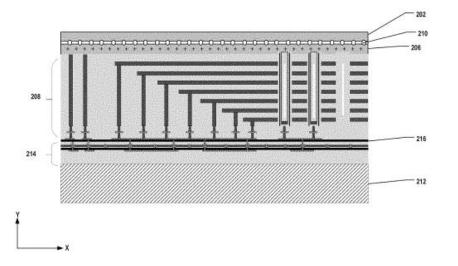

- Warpage: A warpage release layer structure is formed over the interposer substrate and includes at least one organic material layer in direct contact with the upper surface of the semiconductor die and a high CTE material layer formed over the organic interposer (new patent application <u>US20230010707</u>). Another possibility to control warpage is the use of an interposer with warpage-relief trenches in non-routing regions of the interposer (<u>US20220344280</u>). The method also includes depositing a warpage-relief material in the warpage-reducing trenches. The structure of the interposer can be modified in order to manage stress. In the new granted patent TWI787076, **TSMC** claims a method for forming an interposer with redistribution layer structures in adjacent via layers extending in different directions (see also the pending US patent application <u>US20220336359</u>). The via structure connecting the traces of the redistribution layer structures are therefore in different cross-sectional views. Therefore, the effect of CTE mismatch between the device and the substrate may be reduced, and the strain the via structure suffered may be further reduced.

- Speed: In new granted patents <u>US11482497</u> and <u>US11462495</u>, TSMC claim a bridge die for connecting devices dies, which may provide high speed channel between the device dies. Placing a serializer/de-serializer die proximate to a sidewall of a substrate allows a length of electrical pathways to be reduced, thus reducing impedance and RC delay. The use of smaller, separate, interposers also reduces complexity of fabrication of interposers and similarly lowers impedance associated with redistribution interconnect structures and the interposers (see the new patent application <u>US20220415867</u>).

- Process: Organic interposer dicing process is improved to avoid delamination (new patent application <u>US20230023268</u>).

- Hybrid Bonding: The hybrid bonding technique is used by TSMC for connecting electronic devices to redistribution structures (RDLs) as disclosed in the new patent applications <u>US20230012157</u> and <u>US20220381985</u>, and semiconductor die to the dielectric layer of a thermal dissipation structure (see the <u>US20230068578</u>). TSMC is also improving the wafer-wafer bonding via wafer bonding systems and plasma activation (<u>US20230010038</u>, <u>US20230067346</u>).

- TSMC shown IP activity this quarter on 3D-stacked memories. In the new patent application <u>US20220415867</u>, High-Bandwidth Memory dies (HBM) are integrated with a SoC die. To minimize ohmic losses and RC delay, the SoC die and the HBM die may be disposed on an interposer. Reliability of packaged memory dies is improved in the pending patent application <u>US20230035212</u>, where a memory device including a base semiconductor die, conductive terminals, memory dies, an insulating encapsulation and a buffer cap is provided. Buffer caps improve the reliability of the package.

#### **GlobalFoundries** Q4-2022 IP ACTIVITY

GlobalFoundries

| Note: A patent family/patent can    |         |                          |                     |                       |                        |                   |                      |         |  |

|-------------------------------------|---------|--------------------------|---------------------|-----------------------|------------------------|-------------------|----------------------|---------|--|

| belong to multiple segments.        | Q4 2022 | All Fan-Out<br>packaging | FO - Panel<br>level | All 2.5D/3D packaging | Interposer<br>/ Bridge | Hybrid<br>bonding | 3D-stacked<br>memory | OL IEIS |  |

| New patent families<br>(inventions) | 20      |                          |                     |                       |                        |                   |                      | 20      |  |

| Patent families newly granted       | 22      |                          |                     |                       |                        |                   |                      | 22      |  |

| Patents expired or abandoned        | 77      |                          |                     |                       |                        |                   |                      | 76      |  |

• This quarter, there is no noticeable inventions newly published or granted on key advanced packaging technologies. Among the newly published patent families, inventions are more focused on **electro-optics** for which packaging possibilities are described. Other patents focus **on ICs, interconnects, logic and memory**, where packaging possibilities are proposed.

• GlobalFoundries lost IP protection shares in Q4-2022 with 77 newly dead patents. These patents belong to the category "others". We do not describe them, but they are available in the Excel file.

#### OSAT

#### (outsourced semiconductor assembly and test companies)

#### Amkor Technology Q4-2022 IP ACTIVITY

Technology®

| Note: A patent family/patent can    |         |                          |                     |                       | SEGMENTS               |                   |                      |           |  |  |

|-------------------------------------|---------|--------------------------|---------------------|-----------------------|------------------------|-------------------|----------------------|-----------|--|--|

| belong to multiple segments.        | Q4 2022 | All Fan-Out<br>packaging | FO - Panel<br>level | All 2.5D/3D packaging | Interposer<br>/ Bridge | Hybrid<br>bonding | 3D-stacked<br>memory | O LIFE IS |  |  |

| New patent families<br>(inventions) |         |                          |                     |                       |                        |                   |                      |           |  |  |

| Patent families newly granted       | 2       |                          |                     |                       |                        |                   |                      | 2         |  |  |

| Patents expired or abandoned        | 45      | 20                       |                     |                       |                        |                   |                      | 25        |  |  |

- In Q4-2022, Amkor lost invention protection shares in Fan-Out packaging due to the expiration of about 20 US patents belonging to 2 patent families (first published patents US6905914 and US6841874). These two inventions are related to wafer level package, and some members mention Fan-Out traces. These inventions have been carefully kept alive by Amkor over the past 20 years, which shows the importance of these patents to the company. The critical patent family US6905914 (18 US members) discloses a wafer level package and fabrication method with bond pads that are electrically connected to the corresponding first vias without the use of a solder, e.g., without the use of flip chip bumps, and without the need to form a solder wetting layer, e.g., a nickel/gold layer, on the bond pads. This maximizes the reliability of the electrical connection between the first vias and the bond pads, while at the same time minimizes impedance.

- Another critical patent family belonging to the segment "Others" (<u>US6930256</u> and 8 other US members) discloses a semiconductor package having **laser-embedded terminals** in order to provide a **high-density and low cost internal/external mounting and interconnect structure** for integrated circuits.

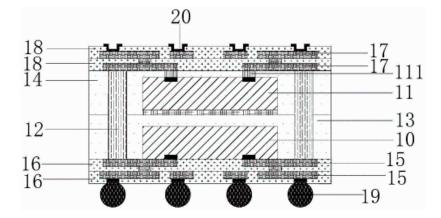

#### ASE Q4-2022 IP ACTIVITY

| AS |  |

|----|--|

|    |  |

|    |  |

|    |  |

| Note: A patent family/patent can    |         |                          |                     |                       | SEGMENTS               |                   |                      |        |  |

|-------------------------------------|---------|--------------------------|---------------------|-----------------------|------------------------|-------------------|----------------------|--------|--|

| belong to multiple segments.        | Q4 2022 | All Fan-Out<br>packaging | FO - Panel<br>level | All 2.5D/3D packaging | Interposer<br>/ Bridge | Hybrid<br>bonding | 3D-stacked<br>memory | QUIETS |  |

| New patent families<br>(inventions) | 64      | 4                        |                     | 9                     | 9                      |                   |                      | 52     |  |

| Patent families newly granted       | 49      | 6                        |                     | 10                    | 7                      | 4                 |                      | 35     |  |

| Patents expired or abandoned        | 106     |                          |                     |                       |                        |                   |                      | 106    |  |

• This quarter, **ASE** had IP activity related to Interposer/Bridge, and more specifically **bridge dies** (new published invention <u>US20220415851</u>, and patent families firstly granted <u>US11508655</u>, <u>US11462484</u>).

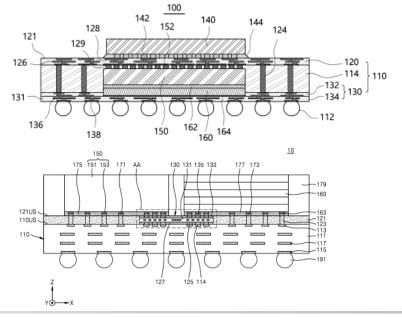

- ASE got 4 newly granted invention in the field of hybrid bonding. Issues related to bond strength are addressed in the new granted patent <u>US11538756</u>. The bonding structure includes a NT-Cu layer having anisotropic crystal structure, which allows for a more uniform thermal expansion at a top surface of the NT-Cu layer. Superior bonding strength and electrical connection between two bonded NT-Cu layers is achieved. Alignment of connections between semiconductor structures in contact is addressed in the new granted patent <u>US11538778</u>, where a semiconductor package includes an alignment material (an organic dielectric material and a notch). In the <u>US11495557</u> a method allows to decrease the bonding temperature process, in order to limit damages on the semiconductor materials when using standard hybrid bonding process. A surface treatment is provided. In the <u>US11502024</u>, ASE claims redistribution layers on two sides of a semiconductor element to provide electrical connections with faster transmission speed and smaller package. The semiconductor active surface and the RDL are connected by hybrid bonding.

- Regarding the Fan-Out packaging segment, reliability improvement of the FO process is claimed in the new granted patent <u>US11515249</u>. The risks of the narrow-inline/space fan-out structure peel-off can be significantly reduced by embedding a portion of the conductive layer in the dielectric layer. Finally, in the new patent family <u>US20220384308</u> published this quarter, an improved FO package is disclosed for structures that include a decoupling capacitor, such as a deep trench capacitor (DTC) die, and an integrated circuit (IC) die. The package allows the DTC die to be electrically connected to the IC die by a shorter electrical path.

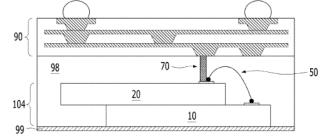

#### **SPIL** Q4-2022 IP ACTIVITY

(C)KnowMade

| _ |   |     |   |

|---|---|-----|---|

|   |   |     |   |

|   | _ |     |   |

| _ |   |     |   |

|   |   | = = |   |

|   |   |     |   |

|   |   |     | - |

| Note: A patent family/patent can |         | SEGMENTS                 |                     |                       |                        |                   |                      |         |  |

|----------------------------------|---------|--------------------------|---------------------|-----------------------|------------------------|-------------------|----------------------|---------|--|

| belong to multiple segments.     | Q4 2022 | All Fan-Out<br>packaging | FO - Panel<br>level | All 2.5D/3D packaging | Interposer<br>/ Bridge | Hybrid<br>bonding | 3D-stacked<br>memory | Oviens/ |  |

| New patent families (inventions) | 10      | 4                        |                     | 1                     | 1                      |                   |                      | 6       |  |

| Patent families newly granted    | 4       | 2                        |                     | 2                     | 2                      |                   |                      | 1       |  |

| Patents expired or abandoned     | 21      |                          |                     |                       |                        |                   |                      | 21      |  |

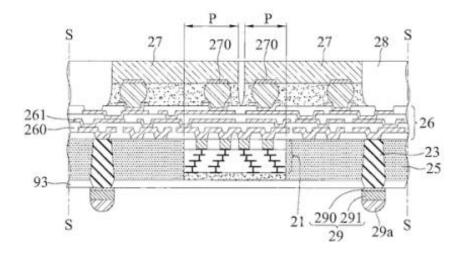

Fan-Out packaging has been the most active segment for SPIL this quarter, with structural improvements of the package. In the new granted patent <u>TWI788230</u>, a local high wiring configuration (member 21) in combination with a local low wiring (carrier structure 26) wiring design (member 21 replaces a portion of the RDL form line layer 261 of the carrier structure 26). The carrier structure 26 not only maintains a high L/S line specifications (e. g., 10/10 microns L/s), but also reduces the number of layers of the connection layers 261 (e. g., less than five layers of line layers 261) to increase the process yield of the carrier structure 26 (or RDL). Thereby effectively reducing overall process difficulty and reducing manufacturing costs.

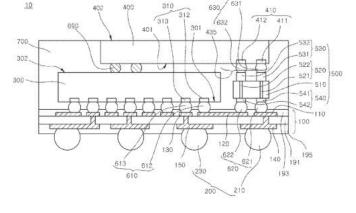

#### JCET Group Q4-2022 IP ACTIVITY

| Note: A patent family/patent can | Q4 2022 |                          | SEGMENTS            |                       |                        |                   |                      |          |  |